物理氣相沉積(PVD)介紹

發布時間:2017-04-01

雖在IC晶片制造程序上,必然會使用到各種不同種類的導體,而低電阻的金屬就常使用在微電子電路的電子訊號連結上。而各類金屬薄膜制作過程,也就成為電子電路必備的制作程序之一。物理氣相沉積(Physical Vapor Deposition)是以物理機制來進行薄膜沉積技術,所謂物理機制就是物質的相變化,如蒸鍍(Evaporation)、濺鍍(Sputtering)。而這種過程無涉及化學反應,因此所沉積的材料純度佳且品質穩定。而PVD的濺鍍制作過程,可以達成快速的沉積速率、準確的沉積厚度控制、精確的成份控制及較低的制造成本。所以濺鍍是目前半導體工業所大量采用的薄膜制作方式,以目前之金屬化制作過程來看:Ti、Ta、TiN、TaN等所謂的反擴散層或是黏合層及導線連接Al/Cu,都可使用物理氣相沉積法來完成。本文將淺略的介紹PVD的種類、原理、先天的缺陷以及克服缺陷的方式,讓閱讀者對PVD有初步的認識。

PVD的種類與原理

1.1、蒸鍍(Evaporation)

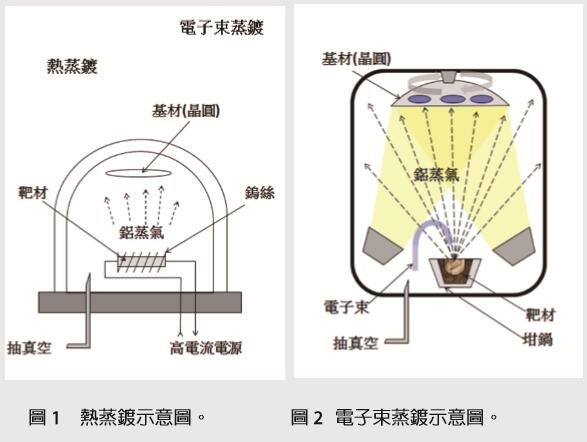

蒸鍍原理(圖1、圖2)是在高真空腔體中,放入所要蒸鍍的材料,利用電熱絲或電子束加熱升溫達到熔化、氣化溫度,使材料蒸發,到達并附著在基板(晶圓)表面上的一種鍍膜技術。在蒸鍍過程中,被鍍物的表面溫度對蒸鍍所形成的薄膜的特性有很重要的影響。基板須要適當加熱,使得蒸鍍原子可以在基板表面自由移動,如此才能形成均勻的薄膜。基板加熱至150℃以上時,可以使沉積膜與基板間形成良好的鍵結而不致剝落。

1.2、濺鍍(Sputter)

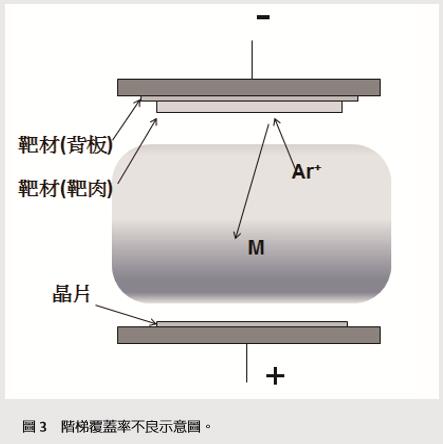

Sputter是利用在高真空的環境下,反應室通入適當的氣體(大多使用氬氣Ar),并控制在適當的壓力下,反應室內的自由電子去撞擊Ar分子,造成Ar的解離,產生二次電子與Ar離子,Ar離子受到靶材上負電位的影響,加速去撞擊靶材,將靶材上的金屬給撞擊下來,并沉積在晶片表面上。(圖3)靶材的冷卻則是當靶材不斷受到高能量(溫度與速度)的Ar離子轟擊,會使得靶材的溫度持續升高,溫度過高將破壞靶材與周邊治具的結合,因此必須冷卻。一般靶材都是用水冷卻,冷卻水流過靶材背面將熱量帶走,達到冷卻的目的。

絕緣材料的濺鍍乃絕緣薄膜須利用射頻濺鍍或反應濺鍍。若采用直流電濺鍍,將造成靶材表面電荷持續堆積而無法濺鍍。電荷持續堆積過量,可能瞬間放電,產生高能高熱,損壞靶材與周邊。例如TiO2、Ta2O3?等。所謂反應濺鍍(Reactive Spuutering)是濺鍍時將反應性氣體加入腔體中進行反應。例如:在氬氣加氮氣的環境下濺鍍鈦,會形成氮化鈦(TiN)。

PVD鍍膜技術特殊效應與現象

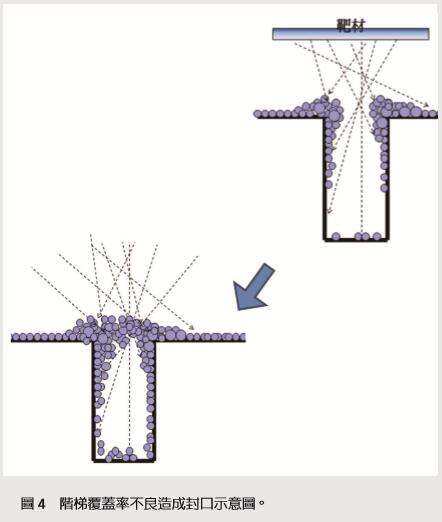

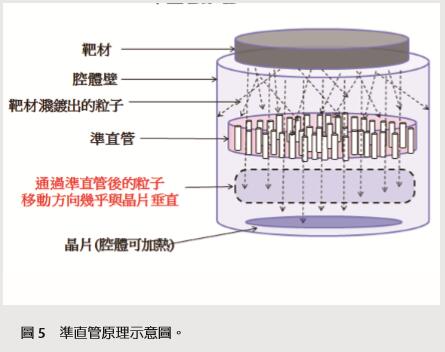

Sputter其主要鍍膜優點是純度高、低溫可形成薄膜,而其最大的缺點就是階梯覆蓋率(Step Coverage)比較差(相較于CVD)。濺鍍本身受到濺射原子多方向與多角度散射的影響下,不易在非水平表面下,得到連續且均勻覆蓋(Conformal)的薄膜。當制作過程線寬極小化的時后,用傳統PVD鍍膜的方式就有其缺陷存在。圖4為階梯覆蓋率不良的示意圖。

階梯覆蓋率改善的方式

2.1、基板加溫:加熱基材表面,使封口時機延后

2.2、使用準直管(圖5)

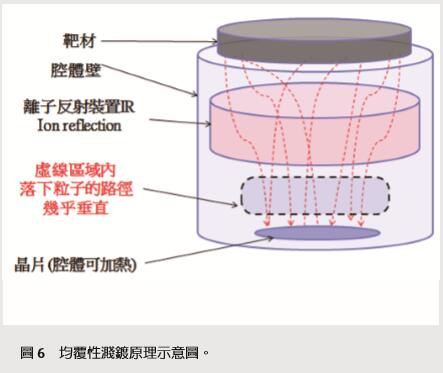

2.3、使用力場將粒子移動方向拉直(圖6)

物理氣相沉積(PVD)是目前在半導體制作過程中,最被廣泛與常態運用于金屬薄膜、金屬氮化物、氧化物的鍍膜技術。雖然在小線寬的薄膜沉積能力,化學氣相沉積有較優的效果,即便如此PVD仍可透過各種不斷創新的制作過程技術與設備去克服小線寬階梯覆蓋率不良的問題。因此物理氣相沉積法仍在半導體制作過程上,依舊占有著舉足輕重、不可或缺的關鍵性角色。目前各項薄膜技術中,PVD成膜速度及薄膜純度等優點,仍是PVD最大的優勢。相信在可預見的未來,半導體及相關電子產業界,物理氣相沉積仍是不可能被取代。

聲明:本站部分圖片、文章來源于網絡,版權歸原作者所有,如有侵權,請點擊這里聯系本站刪除。

| 返回列表 | 分享給朋友: |

- 上一篇:PVD鍍制鈦金屬涂層的特性

- 下一篇:PVD涂層技術的使用為何能占半壁江山?看…

京公網安備 11010502053715號

京公網安備 11010502053715號